本研究ユニットでは,社会に存在する複雑で大規模な組合せ最適化問題を高速に解くソリューションの提案を目標に,アニーリングプロセッサの研究・開発を進めています.これまでの研究にて,「確率的・セルラー・オートマタ・アニーリング」(Stochastic Cellular Automata Annealing: SCA)と呼ばれる新たなアニーリング方式を構築するとともに,それを利用した新しいプロセッサLSI,STATICA(Stochastic Cellular Automata Annealer)を開発しました.本研究の成果は,半導体集積回路のトップカンファレンスInternational Solid-State Circuits Conference(ISSCC) 2020 (2月@米国サンフランシスコ)にて発表されています.

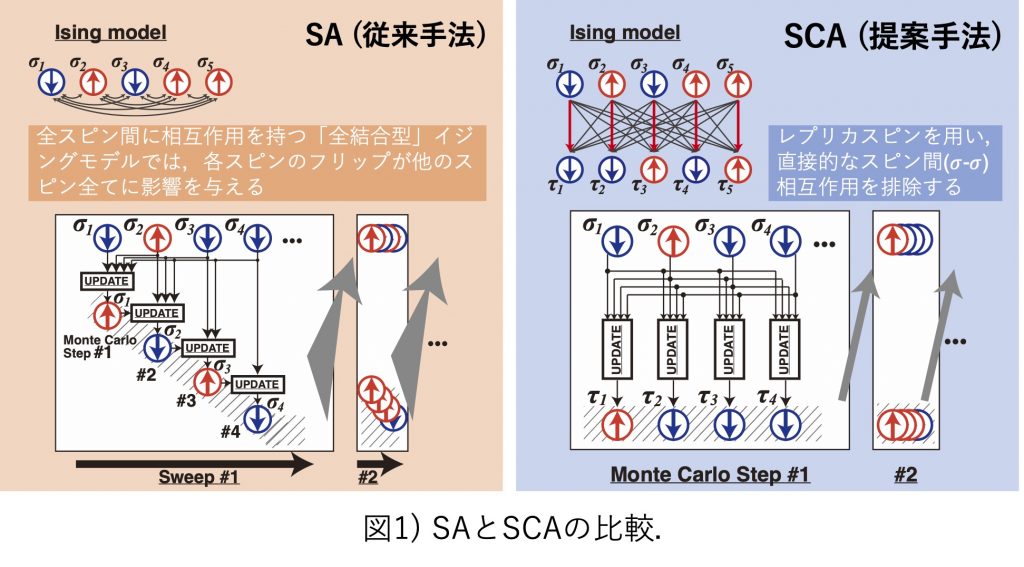

我々が対象とするアニーリングプロセッサは,双安定状態を持つ多数の(擬似)スピンで構成されるイジングモデルの挙動をエミュレートすることで効率的に組合せ最適化問題を解きます.アプリケーション応用を考えると,プロセッサは全スピン間に相互作用を持つ「全結合型」のイジングモデルを扱う必要がありますが,従来のアニーリング方式である「シミュレーテッド・アニーリング」(Simulated Annealing: SA)を用いた場合,スピン更新を逐次的に実行せざるを得ず,並列演算の恩恵を受けにくい問題点がありました.この問題を解決するため,従来とは異なる「全結合型」イジングモデルをベースに,全スピンの並列更新が可能なアニーリング方式としてSCAを提案しました.我々の研究グループは,SCAによってSAと同じ最適解が探索可能であることを数学的に証明し,SCAを用いたアニーリングプロセッサが実現可能であることを明らかにしています.

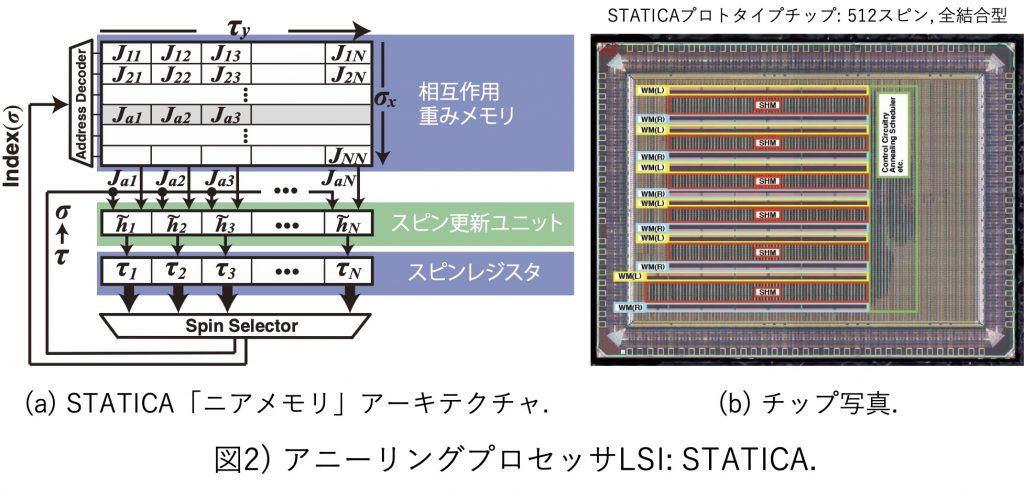

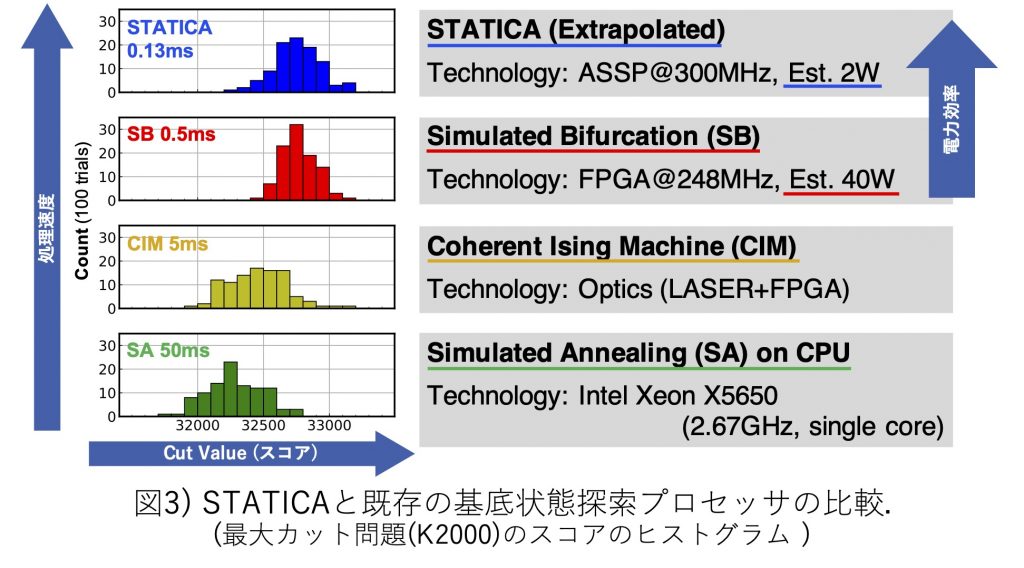

SCAにおける並列スピン更新は,更新対象のスピンに関係する相互作用の値を読み出し,現在のスピン状態と演算することで実行されます.すなわち,相互作用の値が記憶されたメモリから並列に値を読み出し,メモリに付随したロジック回路で並列演算することにより,SCAの演算処理を効率的に実行することができます.このようなメモリのすぐ近くで演算をおこなう「ニアメモリ」型アーキテクチャにもとづいて開発したアニーリングプロセッサLSI「STATICA」は,2020年現在,既存プロセッサと比較して,アニーリング速度・消費電力・解精度のいずれにおいても高い指標を達成することができています.

SCAにおける並列スピン更新は,更新対象のスピンに関係する相互作用の値を読み出し,現在のスピン状態と演算することで実行されます.すなわち,相互作用の値が記憶されたメモリから並列に値を読み出し,メモリに付随したロジック回路で並列演算することにより,SCAの演算処理を効率的に実行することができます.このようなメモリのすぐ近くで演算をおこなう「ニアメモリ」型アーキテクチャにもとづいて開発したアニーリングプロセッサLSI「STATICA」は,2020年現在,既存プロセッサと比較して,アニーリング速度・消費電力・解精度のいずれにおいても高い指標を達成することができています.