深層ニューラルネットワークは,時に人間を超える精度で画像分類などを行うことができるほどに発展し,広範に用いられ始めています.その基本となる計算処理は,センサなどから得られた入力データと学習によって獲得された係数データとの多量の内積計算から成り立ちます.近年のニューラルネットワークの急発展の背景には高負荷な処理を実用的な時間で行えるようになった計算機技術の進歩が挙げられますが,発展を続ける最新のニューラルネットワークアルゴリズムの要求処理はどんどん複雑になっています.そのため,ニューラルネットワークの処理に特化して効率と速度を求める専用アクセラレータの研究が活発に行われています.

本研究室では,処理の複雑さと要求メモリ容量を落とすことのできる量子化ニューラルネットワークアルゴリズムを採用したアーキテクチャや,多くのアルゴリズム・ネットワーク構造に遍在する処理要素に着目した汎用なアクセラレータの研究に加え,ハードウェア処理を見越した構造により効率と精度の両立を目指すアルゴリズムの研究の両面から取り組んでいます.

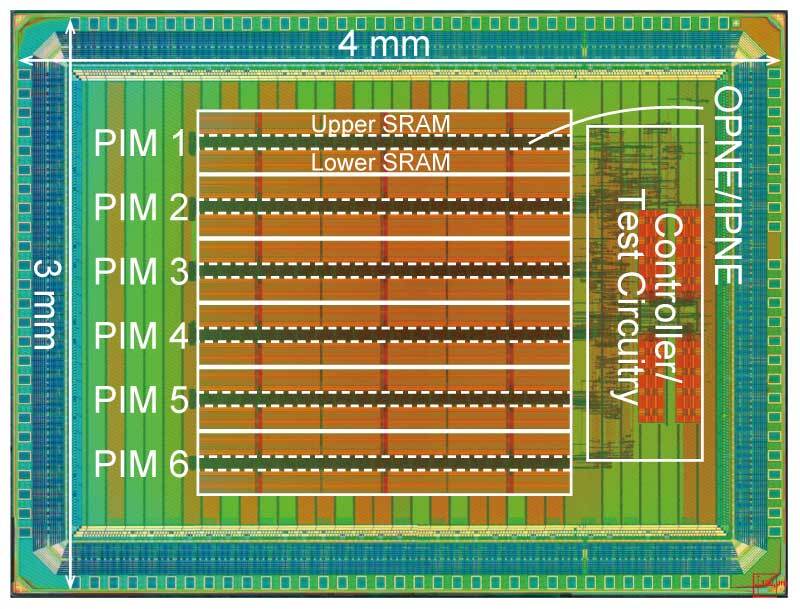

一例として,前身研究室での成果ですがニューラルネットワーク計算で使用する全ての入力・出力値と係数の値を1ビットの±1で表現するBinary Neural Networkのアルゴリズムを用いることで,高密に係数を保持する内蔵SRAMにサンドイッチされた小さな処理回路で全ての計算を完結する高効率なアクセラレータ “BRein Memory” を発表しました.

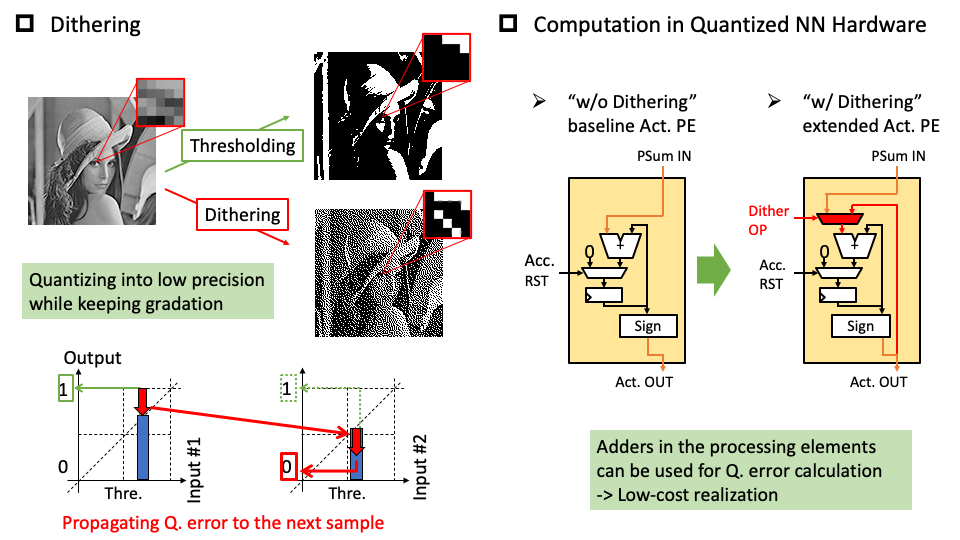

また,Binary Neural Networkをはじめとする量子化アルゴリズムの処理手順に着目し,画像処理で広く使われるディザの処理を取り入れることでハードウェアコストをそのままに精度を向上させるアルゴリズム “Dither NN” を提案しています.