ArtIC is aiming to develop an innovative annealing processor that solves combinatorial optimization problems efficiently. Our research group has constructed a novel annealing methodology, called SCA (Stochastic Cellular Automata Annealing), and developed a full-digital annealing processor, STATICA (Stochastic Cellular Automata Annealer). We presented the LSI chip of STATICA in the International Solid-State Circuits Conference (ISSCC) held in San Francisco in February 2020.

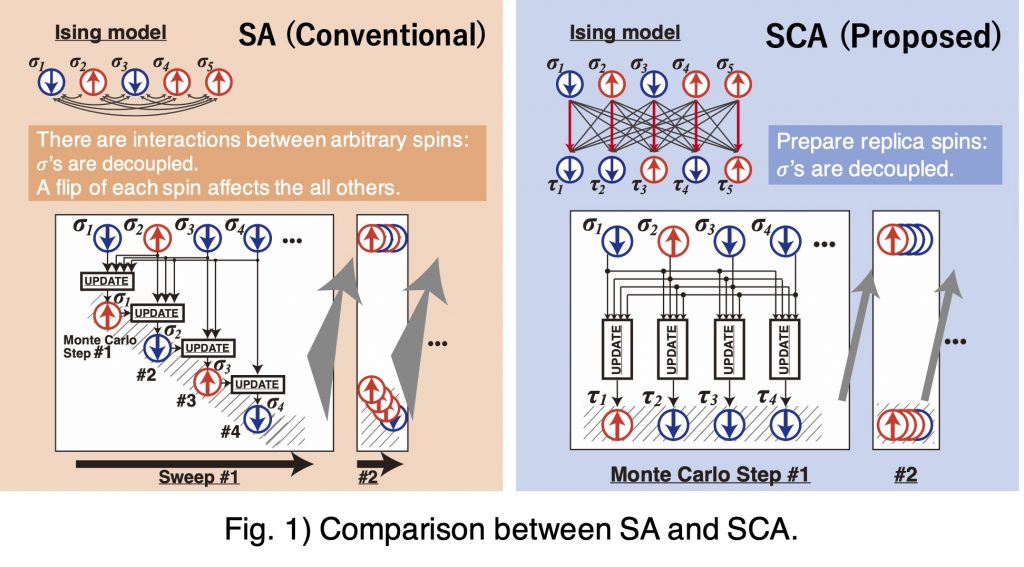

Annealing processors, or annealers, efficiently solve a combinatorial optimization problem by emulating the behavior that leads an Ising model to the ground state. While supporting a fully-connected Ising model is mandatory for dealing with realistic optimization problems, previous annealers, which are typically based on SA (Simulated Annealing), had a problem such that the spin update process is inherently serial. We solved this problem by constructing SCA that utilizes a different type of fully-connected Ising model. In SCA, we can update all the spins in parallel. Note that our group has mathematically studied the behavior of SCA, and found that SA and SCA reach the same ground state under certain conditions.

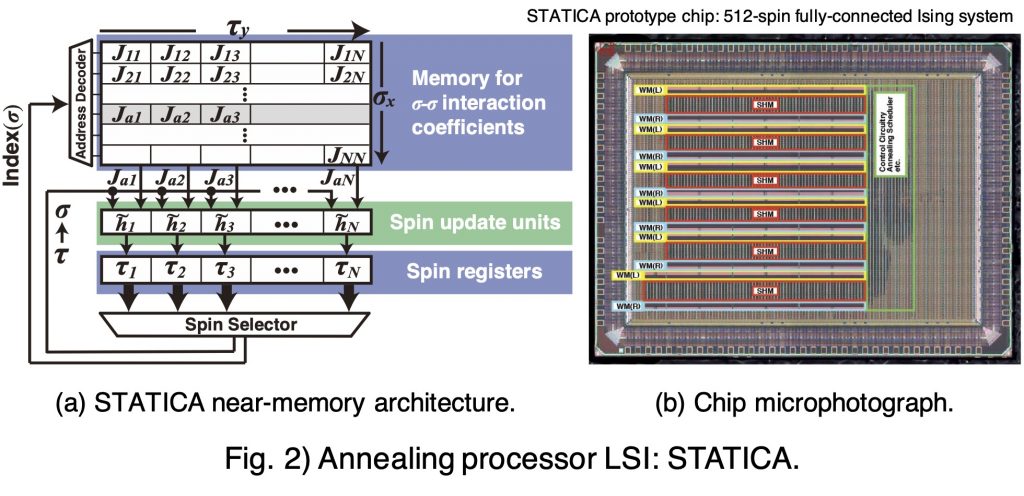

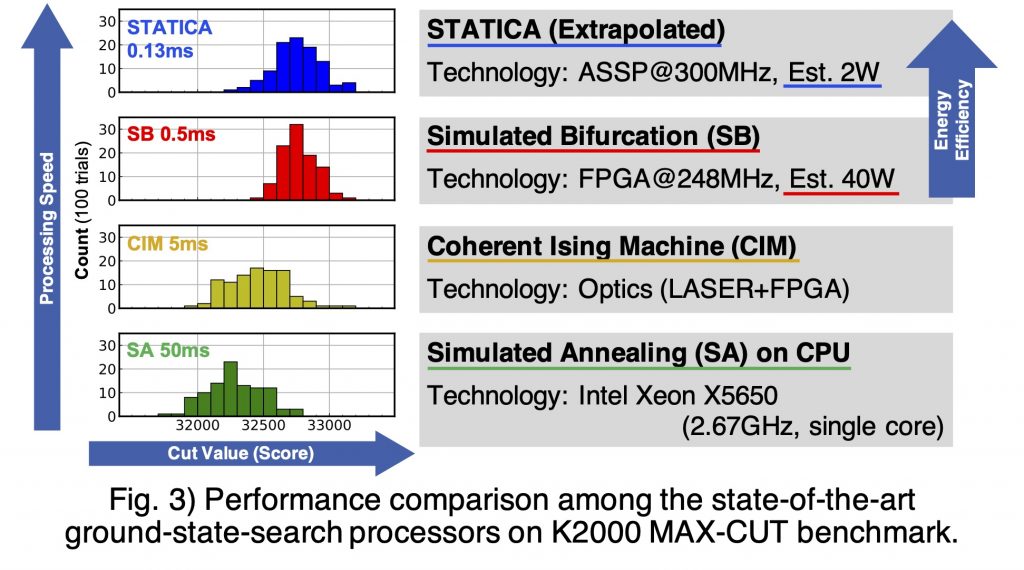

The parallel spin update process in SCA is performed by operations for current spin states and spin-spin interaction coefficients. Since we need to store the interaction values in on-chip memory blocks, the operations can be accelerated by reading out the values in parallel and then executing them in parallel with a series of circuits placed very close to the memory block. Our annealing processor, STATICA, has been developed based on this near-memory architecture. When solving an optimization problem represented as a fully-connected Ising model, STATICA has achieved the best performance among the state-of-the-art ground-state-search processors.