# 東工大・情報通信系 大学院説明会本村・劉研究室 紹介スライド

### 2021年 3月 25日

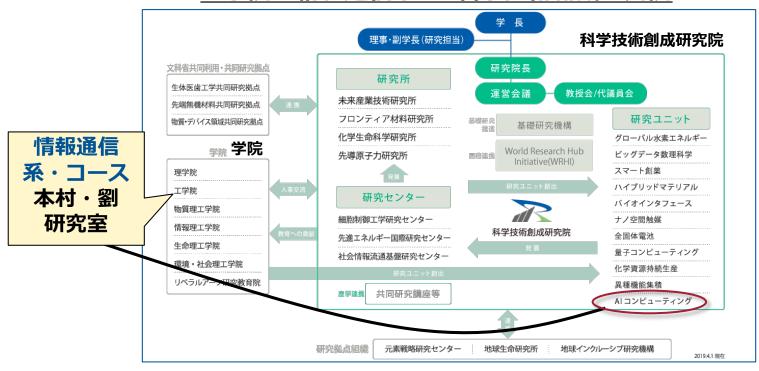

東京工業大学 科学技術創成研究院 AIコンピューティング研究ユニット (ArtIC) 情報通信系 本村・劉 研究室

# AIコンピューティング研究ユニット: ArtIC

2019年4月 に発足 2020年4月からフル メンバで活動中

すずかけ 台キャン パス J3棟 17F

### http://www.artic.iir.titech.ac.jr

ArtIC のミッション

新たな AI プラットフォームの創出

共通基盤コンピューティングアーキテクチャ 自律性・安全性・エネルギー効率・コスト効 率の高いハードウェア基盤の実現

## ArtICの成り立ち

#### 工学院・情報通信系 と 科学技術創成研究院

### <u>Artificially Intelligent Computing Research Unit</u>

もう一つの意味: ArtなIC

=> 素敵なハードウェア

=> ソフトとハードの協調研究

## 2020年代: コンピューティングの新時代

# AIコンピューティング

人工知能革命の急進

Ш

ポストノイマン時代

情報処理ハードウェアに 変化のチャンスが到来

- Pull -

ムーアの法則の終焉

Ш

ポストムーア時代

情報処理ハードウェアが 変化せざるを得ない

- Push -

大きな成果を上げるチャンス 社会的に大きな意味のある研究

### ArtIC: 研究ターゲット

人工知能(AI)応用の急速な拡大 「**コントロール**駆動からデータ駆動へ」 **計算機アーキテクチャの革命**

<u>大量データの学習 →</u> 強力な推論・識別・予測能力

深層ニューラルネット ・ディープラーニング 説明性・制御性の高さと低学習負荷の両立

アニーリング計算機 \_\_\_\_(非量子) 統計的機械学習 ▼ (アンサンブル学習等)

構造型情報処理アーキテクチャ として共通基盤化

アルゴリズム理解 => アーキテクチャ研究 => ハードウェア実現

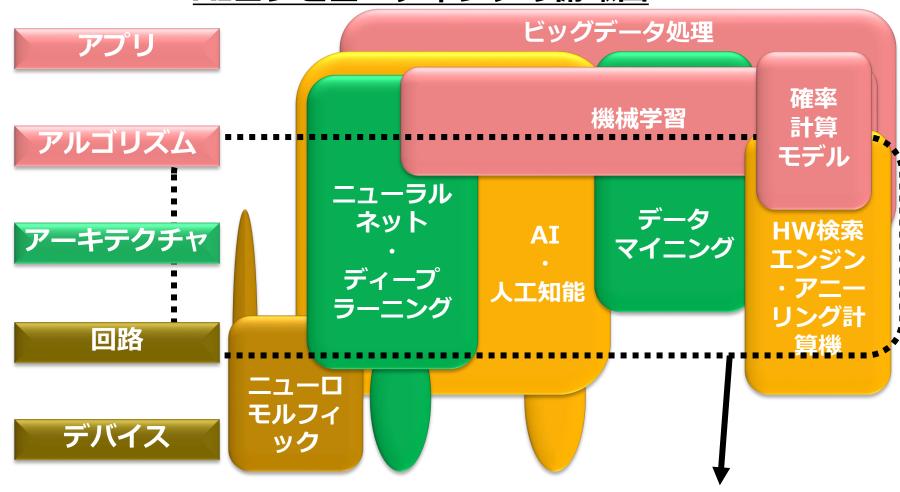

### ArtIC: 研究分野・研究レイヤ

### AIコンピューティングの俯瞰図

これら広範囲のAIコンピューティング群を加速する アーキテクチャの研究を推進

### 研究ユニット教員の紹介

### <u>本村</u>

局

速処理·省

工

両立

'87 京大理学部修士'96 京大工学博士'87-'11 NEC研究所'11-'18 北大'19- 東工大

LSIのオリンピック ISSCC2018で、量 子化ニューラルネッ トチップの発表

4千人参加の最高峰会議

遠色な繋ずに183mmままままで 世界初: 二値化二ユーラ

日経新聞 17/9/18

日朝刊に掲載

AI支えるテクノロジー <sup>⑤専用半導体</sup>

A I の普及には新しい半導体が必要

CPU あらゆる計算をこな (中央演算 せる。AI向けの計

向けの応用に強み

算は苦手

A I に特化 高速処理と省エネを

は、足し算や引き算の手順夕を扱うAIへの応用で

現 処理装置)

(画像処理

した半導体 両立

発目間の が連信 では、 が連信

ルネットチップ

日本初:深層ニューラル

ネットチップ

多くのシンポジウム でAIハードウェアの 招待講演

### 劉

'87 京大理学部修士 | '07 京大情報学修士 '96 京大工学博士 | '13 阪大情報科学博士

′13-19 阪大 ′19/10- 東工大

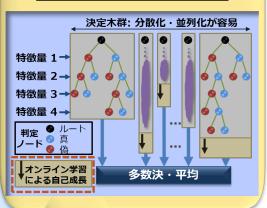

ブースティング

決定木の並列ア

クセラレータ

汎用物体認識シス テム(FPGA利用)

実装

ミス 率\*

フレーム レート

処理 検出窓数

既存 SVM

46%

Full HD 60 fps

6,284k/秒

既存 ACF

17%

VGA 30 fps

1,972k/秒

案 ACF 17% Full HD 170 fps 112,501k/利

#### FPGA 実装

- 。 Xilinx ZC706 評価ボード

- 。1,024並列: M=8,2次元方向8x16

- 。6.6倍x128並列=845倍高速化

#### リソース使用率

| Slice        | 32Kb BRAM | DSP     |

|--------------|-----------|---------|

| 18,904 (35%) | 186 (34%) | 0 ( 0%) |

#### 識別速度

。 歩行者識別: Full HD 350 fps

BDT: ブースティング決定木

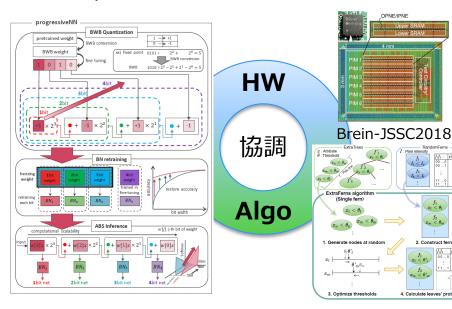

## 近似計算によるディープラーニング

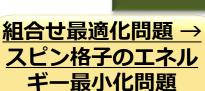

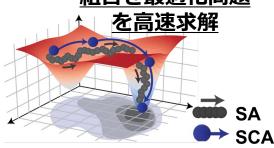

# 最新の研究成果: アニーリングプロセッサ

- 組合せ最適化問題は社会のあ らゆる場面に存在

- ✓ 物流、創薬、工場、広告、交通 、機械学習、集積回路設計...

- 選択肢が指数関数的に増大(組 合せ爆発)

- 精度の高い**ベター**な解を**高速** に得る計算技術のニーズ

$$H(\boldsymbol{\sigma}) = -\sum_{(i,j)\in E} J_{ij} \, \sigma_i \sigma_j - \sum_{i\in V} h_i \sigma_i$$

二値変数の二次関数

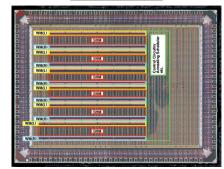

#### LSIのオリンピックISSCC2020で発表

#### STATICA CHIP

### **IEEE Spectrum**

#### 日経新聞

Novel Annealing Processor Is the **Best Ever at Solving Combinatorial Optimization Problems**

14 Apr 2020 | 17:00 GMT

疑似量子計算チップ、東工大など開発 渋滞解消・創薬に応用

2020/2/17付 [有料会員限定]

②保存 ☑共有 局印刷 衛 (1) ★ (7) その他▼

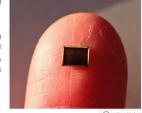

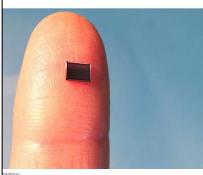

東京工業大学や北海道大学、日立製作所、東京大学などは共同で、量子コンピューター の計算を疑似的に再現して、組み合わせ問題を高速で解くことのできる半導体チップを 開発した。計算を並列で処理できる理論を考案し、数ミリ角のチップを試作した。従来 法よりも計算が約4倍速く、消費電力は約60分の1になった。量子コンピューターよりも 先に、渋滞の解消や創薬、材料開発などで応用できるとみている。

成果は米サンフランシスコで開催される半導 体の国際会議「ISSCC」で発表する。

既存のコンピューターを超える計算能力を持 つ次世代計算機として量子コンピューターが 注目される。現状では極低温まで冷やしたり 複雑な配線が必要だったりするため、装置が 大がかりで計算も安定しない。

既存のコンピューターを使い、量子コンピュ ーターの計算方法をまねる技術が注目を集め る。様々な組み合わせの中から最適解を探す 「組み合わせ最適化問題」の計算を得意とす

数ミリメートル角の半導体チップで量子コンピューターを模

小型化や安定した計算、より大規模な計算に対応できると期待されている

ngineers say their CMOS processor bests ologies in solving the traveling salesman drum and other complex puzzles

years, IEEE Spectrum has spotlighted several new ng combinatorial optimization problems.

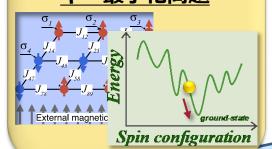

### 最新の研究成果:機械学習

- 深層ニューラルネットワーク・決定木 アンサンブルは様々な応用分野で実用

- 画像認識,音声認識,自然言語処理, 意思決定,…

- 学習・推論にかかる計算量・消費電力の問題

- 高い精度の予測を低計算量,低電力, かつ,高速に行う技術への要求

スケーラブルネットワーク Progressive-CANDAR2020 決定木アンサンブル ExtraFerns-CANDAR2020

#### DNNアクセラレータの研究

### 機械学習アルゴリズム

### <u>CANDAR</u> 2020発表(2

ExtraFerns: Fully Parallel Ensemble Learning Technique with Non-Greedy yet Minimal Memory Access Training

Shungo Kumazawa, Kazushi Kawamura, Thiem Van Chu, Masato Motomura, and Jachoon Tokyo Institut: of Technology, Yokohama, Japan

ProgressiveNN: Achieving Computational Scalability without Network Alteration by MSB-first Accumulative Computation

Junnosuke Suzuki, Kota Ando, Kazutoshi Hirose, Kazashi Kawamura, Thiem Van Chu,

Tokyo Institute of Technology, Yokohama, Japan Email: {suzuki.junnosuke, ando.kota, hirose.kazutoshi, kawamura, thiem, motomura, yu.jaehoon}@artic.iixtitech.a

Above-Computational validities glaves present descriptions are sense with studies great extension and consultance with studies great contential of possible resources. The paper propose a significant consultance of affects being validities accommission for tensions of affects being validities accommission for retination (Aller Morros, one land international for Nervinsian Facilities (Aller Morros, one land international for Nervinsian Facilities and Aller Morros, one land in the studies of the retination for Aller Morros, one land in the studies of the retination o

I. INTRODUCTION

The availability of neural networks on edge devices provides a promising solution to privacy, network connectivity, and real-time responsiveness issues in applying neural networks into healthcare, robotics, vehicles, and industries of urpopulated areas. Since neural networks require a large ansumost of count of the networks and the part and the new control of the networks of the new control of the new countries of the new countries of the new countries of the new countries and the new countries and the new countries are not new countries and new countries are new countries and new countries are new countries and new countries are not never the new countries are not never the new countries and new countries are new countries.

Under severe constraints of computation resources and power communition on only devices, computation already is the key to exploiting the benefits of neural networks. Quant to the key to exploiting the benefits of neural networks. Quant local power has been already to the constraints in exchange for scarrificat devices to satisfy the constraints in exchange for scarrificat security. The power power is the constraints in exchange for scarrification constraints and the constraints in exchange for scarrification security. The constraints in exchange for scarrification (1)1-[91]. These methods opinize network models to perform the less with a quantity of the constraints of the constraints. There is no doubt that they archived constraints presently, but they still constraints of the constraints of the constraints of the object to the constraints.

For inference, edge devices can save more power consumption without accuracy drop by adjusting their computation amount according to task difficulty, i.e., less computation for

rig. 1. Advantage or computational scatterity or dege newton: turce difficulty depends on tasks, and low computational inference is enough understanding tasks. For applications using sequential data such as autiovideo, it is possible to decide proper computation cust based on the previinference result. By adaptively adjusting computational cost, edge devices some more enerty consumption.

easy tanks and more computation for hard tasks, as it in fig. 1. Adaptive interexc., set the messages, i. a proposed control and propos

for anotes that plothesis, we projected a statupe set scale where the scale were proportionally a statupe set scale when the proportion of the proportional propo

ordge devices are not fancy muchine learning algorithms now but suppring cost of superform nearant networks for tabular data. Compared anothers, which are central revows, they note only a few parameters and a vacant tree in sectural revows. The proof of the proposal proposal in the control of computation. These are suitable features for trial on ordges, yet there is still room for improvement in such as proof to the proof of the p

nodes by randomly selecting attributes and generating thresholds. This node generation largely-tendees off-chip memory oblication and the dominant facebre of power consumption. After that, as random/Ernsi does, it builds ferms that are the constraint of the control of the con

The contributions of this paper are summarized as follows.

• We propose an edge-oriented decision tree ensemble that requires an extremely small amount of off-chip memory

requires an extremely small amount of off-chip memor accesses.

ExtraFems conducts non-greedy optimization in paralle

which leads to performance improvement.

This paper also shows that Dirichlet prior, used in randomFerns, is dispensable through experimental results.

domferns, is dispensable through experimental results. The paper is structured as follows. Section II briefs the features of conventional decision tree ensembles. Section III describes the details of the proposed extraferms based on them, and then Section IV and V show preliminary experimental results and evaluation results. Finally, Section VI concludes this rurer.

II. RELATED WO

Decision tree ensembles are statistical machine learning algorithms, which use decision trees as base learners. As thorn in Fig. 1, a decision tree consists of internal modes, transches, and leaf modes. Each of them represents a test on an attribute, the test's outcome, and a class labellan expected outcomes and the state of the

This section briefly describes four ensemble algorithms used designing extraFems: randomForest, extraTrees, randomns, and rFerns. Here, randomForest and extraTrees are

<u>IJNC</u> 投稿中(2件)

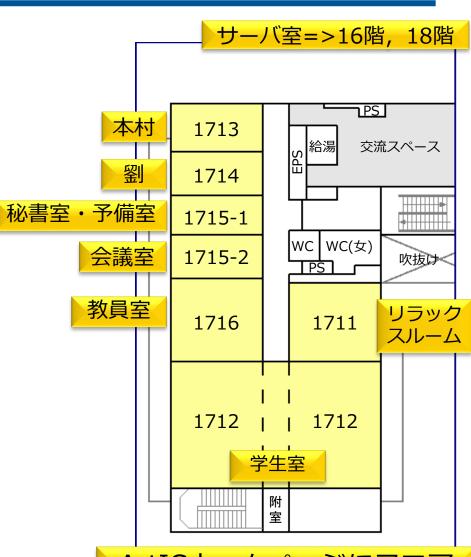

# ArtIC人員・居室構成 (21年4月)

#### 本村研 劉研

|      |       | <u> </u> | <u>亚1 h/ l</u> |  |

|------|-------|----------|----------------|--|

| 教員   | 教授    | 本村       |                |  |

|      | 准教授   |          | 劉              |  |

|      | 助教    | ティエム     |                |  |

|      | 特任助教  | 川村, 5    | 川村,安藤          |  |

| スタッフ | 技術支援員 | (募集中     | (募集中)          |  |

|      | 秘書    | 2名       |                |  |

| 学生   | D3    | 1名       |                |  |

|      | D1    | 1名       |                |  |

|      | M2    | 3名       |                |  |

|      | M1    | 5名       |                |  |

|      | B4    | 3名       |                |  |

ユニット

一体運営

ArtICホームページにフロア 紹介ビデオがあります

### ArtICの研究レイヤ

#### 技術レイヤ

「論理」を相手にする世界

用途に応じてアプリを設計する ンフト ソフト利用環境を構築する ArtIC ソフトとハードの分担を決める の研究 レイヤ LSIの全体構成を決める LSI(Tr数千万個)を設計する 21 ゲート回路(Tr数個)を設計する トランジスタ(Tr)を作る 薄膜等やPN接合を作る

「物理」を相手にする世界

#### 身に付くスキル・知識 (例)

機械学習 アルゴリズム 画像処理 アルゴリズム

ディープラーニング(人工知能)

学習環境構築・ GPU活用 組み込みシステム設計

プロセッサアーキ

非線形・近似計算理論・応用

柔らかいHW (動的再構成LSI)

信号処理

デジタル回路・Verilog設計

FPGA設計・利用

LSI設計

### 最後に…

- □ 本資料は、研究室HPの入学志望者向け情報のページに載せる予定です

- □ ユーチューブチャネル (研究室HPからリンクあり/Artic 東工大で検索可能)

- https://www.youtube.com/channel/UCJY897-DXhrnfMWC4gYIwFw

- LSI設計やFPGAを用いたハードウェア設計に興味を持つ皆さんの ArtICへの参加を歓迎します

- 特別な知識は求めません。この分野の研究に対する意欲を期待します

- 基礎知識が身に付くよう、輪講や研修を行います

- □ 二研究室で共同運営しており、研究ユニット内に垣根はありません

- 居心地よい環境づくりを心掛けています

- <u>一線級の国際会議</u>で発表できるグループを目指しています

- □ 近未来の社会ニーズに即した、実戦的な研究活動を主体としています

- □ 従って、実社会で役立つスキル・知識を身に着けることができます

- □ 産学連携、大学間連携、国家プロジェクト参画を活発に進めています