# AIチップ:世界の研究動向と 東工大の研究戦略

2019年 10月 11日

東京工業大学 科学技術創成研究院 AIコンピューティング研究ユニット (ArtIC) 本村 真人

# 講演者の自己紹介

- 2011年3月まで、NECにおいてLSIアーキテクチャに 関する研究開発と事業化に従事

- 並列プロセッサ、メモリ-ロジック密結合型LSI、etc.

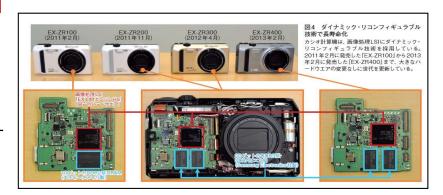

- **動的再構成プロセッサ(DRP)**の研究開発と事業化

- □ 入り口から出口まで: デジカメに搭載

- □ ルネサスエレ社が事業拡大中

- ・AI処理向け技術開発中

- '91-92: MIT客員研究員

- □ データフローアーキテクチャ

- 2011年4月に北大に転任

- 人工知能処理向けLSI、リコンフィギュラブルHW技術などの研究

- 2019年4月に東工大に転任

- AIコンピューティング研究ユニット(略称 ArtIC)を立ち上げ中

# 「人工知能(AI)革命」の急進

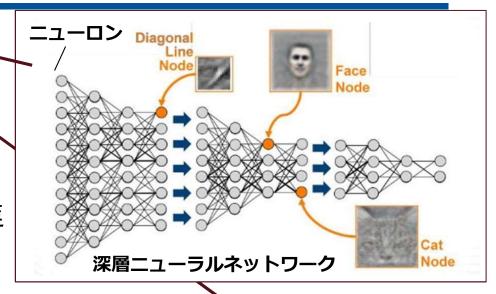

■ 2012年: Googleの猫

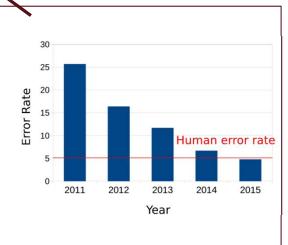

■ 2015年: 人間以上の画像

認識能力を達成

■ 2016年: アルファ碁

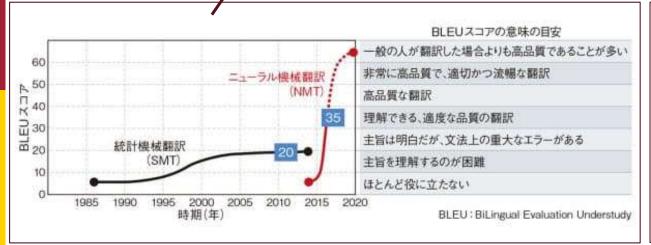

■ 2018年: 自動翻訳技術が

実用レベルに到達

日経新聞 9/24記事 (オリジナルは情報通信機構のデータ)

ImageNet コンペティション

人工知能、AI、ニューラルネット: <mark>敬遠</mark>から**熱狂**へ大転換

# ※ Google画像検索結果から写真をピックアッフ

# AIが変える我々の暮らし

自動運転

ロボティクス

機械翻訳

広告

自動通訳

問題解決・予測

AI時代 := AI処理ワークロードが爆発的に増大する時代

ビッグデータ

+

AIコンピューティング

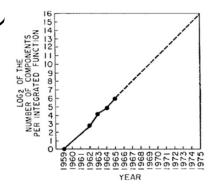

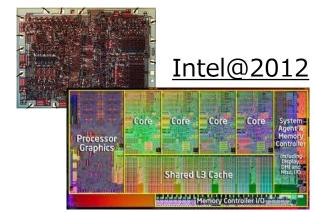

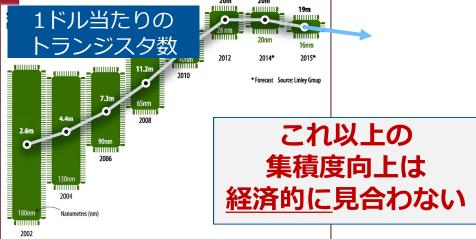

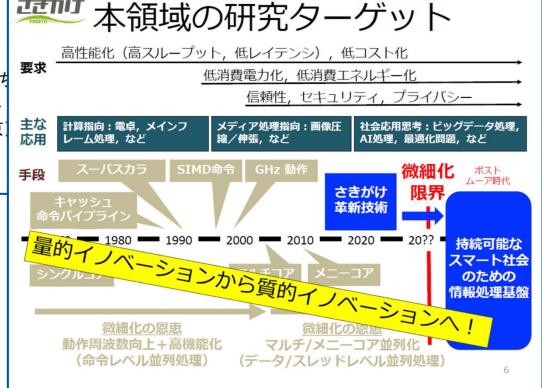

# 「ムーアの法則」とその終焉

- 「ICの集積度は18か月で2倍になる」

- インテル創設者ゴードン ・ムーアが1965年予測

- 50+年間、ICT社会の 発展を支えた基本原則 (2<sup>35</sup> 倍 = 160億倍)

### Intel@1971

# 経済限界

What is Next Exponential?

# 二大潮流のシンクロニシティ

# 情報処理ハードウェアの革新

人工知能革命の急進

П

ポストノイマン時代

情報処理ハードウェアに 変化のチャンスが到来

- Pull -

ムーアの法則の終焉

Ш

ポストムーア時代

情報処理ハードウェアが 変化せざるを得ない

- Push -

引く力 と 押す力

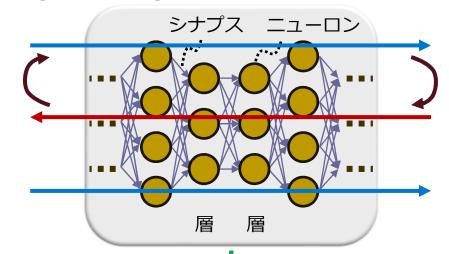

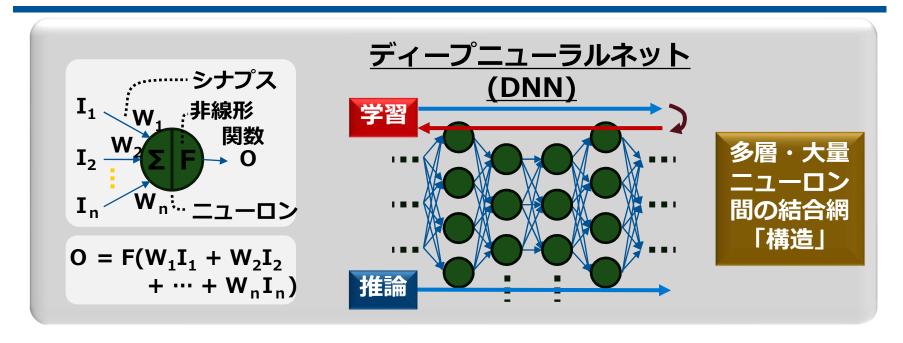

# ディープラーニングの基本

# 深層(ディープ)ニューラルネットワーク

学習

推論

- 既知データで伝搬と逆伝搬を反芻

- 所望の結果に向けてシナプス値調整

- **未知**データを<mark>伝搬</mark> させ結果を出力

高速な計算 ハードウェア

正帰還ループにより 爆発的に発展

大量のデータ

# 情報処理技術への影響: ソフトウェアの視点

ディープラー ニングの本質

「誤差を最小にするように係数を少し づつ学習する作業を延々と繰り返すこ とで機能を獲得できる」という発見

Before DL-

After DL –

かなりの 部分の処理が シフト

専門家の手による 精緻な設計と組立 大量のデータが穿つ ことによる創発的造型

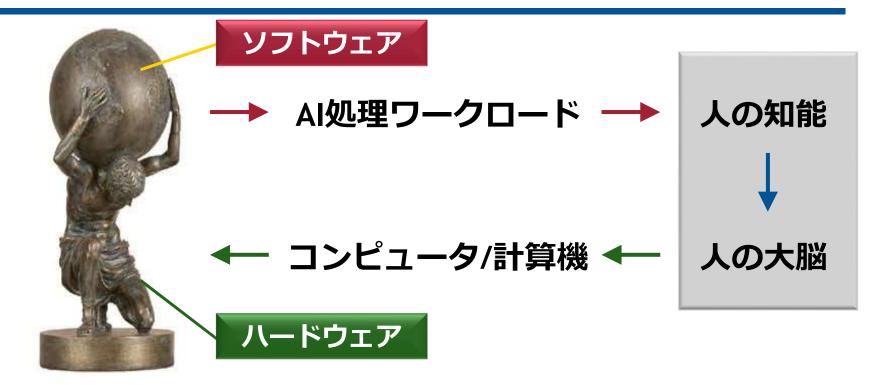

# AI時代にハードウェアはどうあるべきか?

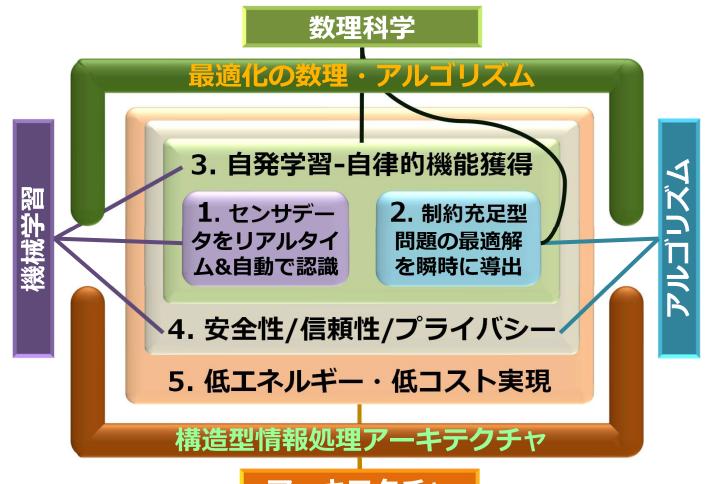

# AIコンピューティングの命題

果たして何を計算するのか? どう計算すればよいのか?

# ワークロードと処理効率の相関

# 計算機と大脳のエネルギー効率比較

高速計算機 (20万W) 大脳 (20W)

囲碁

仮想実行

ネイティフ 実行 直観的・知能的な情報処理では、大脳の方が1万倍の高エネルギー効率

論理的・計算的な情報処理では、<u>計算機の方が1億倍</u>の 高エネルギー効率

ハード ウェアの 基本構造

演算器 神経回路網

得意な情報処理領域では それぞれ相手を圧倒

処理内容と処理構造の適 合度合いが重要

AI処理ワークロードに寄り添うコンピュータが必要

# AI処理:= 構造型情報処理

- □ 大規模なグラフ構造の並列処理

- □ DNN以外の多くのAI処理も同様に<mark>構造型</mark>

- グラフ処理

- 広い範囲の機械学習課題

- □ データマイニング、分類・推定、ベイジアンネット、etc.

- 組合せ最適化問題 (エネルギー関数の最小化で表現できる問題)

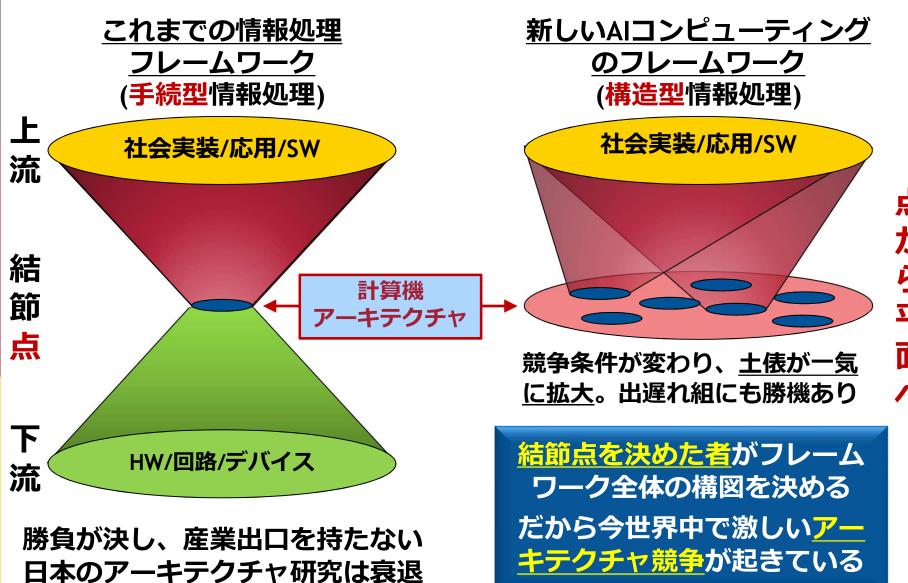

# アーキテクチャ: 手続き型から構造型へ転換

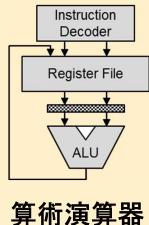

# 「手続き型」情報処理

「コントロールフロー型」 「フォンノイマン型」

1949

- 処理<u>手順</u>をプログラム

- 逐次ネイティブに実行

処理 指示 演算器

DNN興隆で 起きる パラダイム シフト

情

報

処

理

の

道

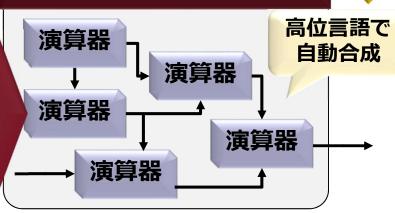

# 「構造型」情報処理

「データフロー型」 「リコンフィギュラブルHW型」

1946

接続を手動で切替

- 処理構造をプログラム

- 並列ネイティブに実行

左脳

← アナロジー →

右脳

# 情報処理ハードウェアへの影響

# 大規模データ

- ニューラルネット構造をハードウェアに写像

- □ 入力データを流し込み結果を抽出

- □ 膨大な単純演算=>大量の並列性が存在

# AIコンピュータ (アクセラレータ)

# メモリ

- □ 重み係数構造情報を格納

- プロセッサに直結

- 🗖 大量・高速の読み出し

# 有用な知見

予知予測、法則性、 特異値、分類、etc.

# 点から平面へ

# 計算機アーキテクチャ研究の黄金期

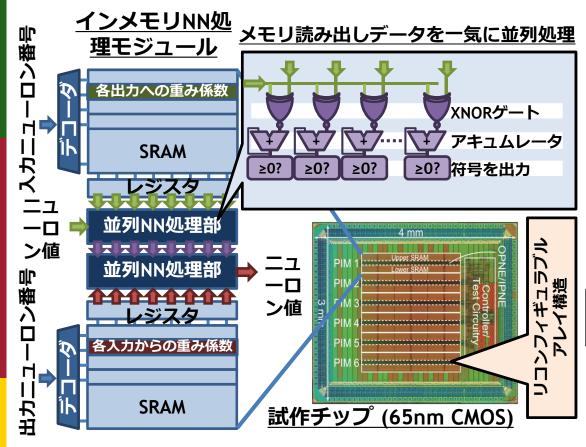

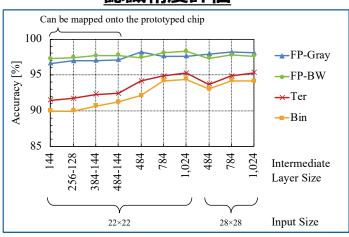

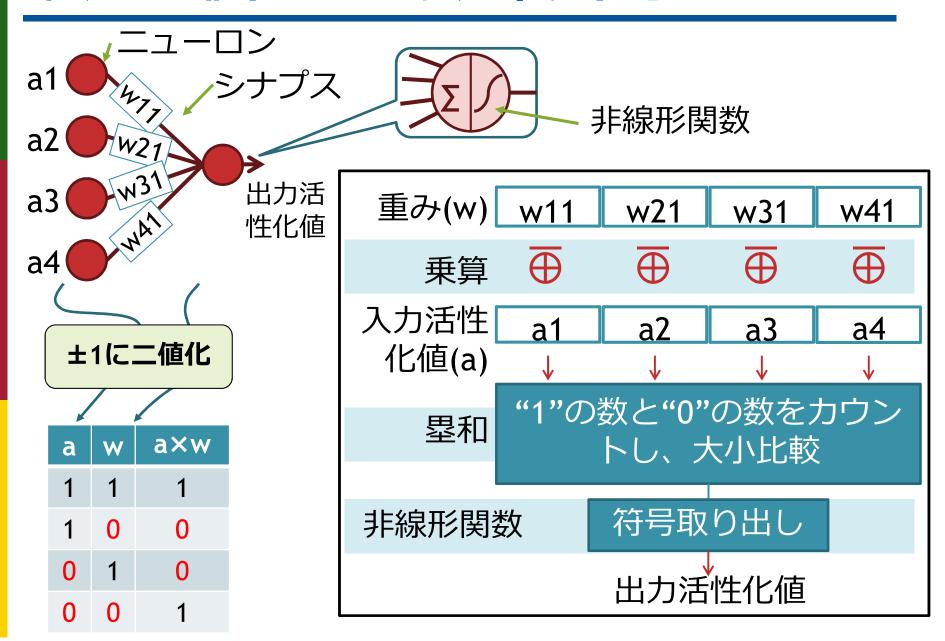

# 実例-1: 本村G 二値化DNNチップ

### CPU等との比較 (手書き文字認識)

|                    | BRein<br>Memory | FPGA | GPU | CPU |

|--------------------|-----------------|------|-----|-----|

| エネルギー効率<br>対CPU相対比 | 2.6万            | 33   | 9   | 1   |

### 認識精度評価

13 layers, 4.2K neurons, and 0.8M Synapses, 1.4TOPS at 0.6W

# <u>VLSIシンポジウム</u> で発表 (17年6月)

世界初の二値化・三値化 DNNチップ。GPU比3K倍の エネルギー効率を実証。 日経新聞等掲載

# 補足: 二値化二ユーラルネットとは

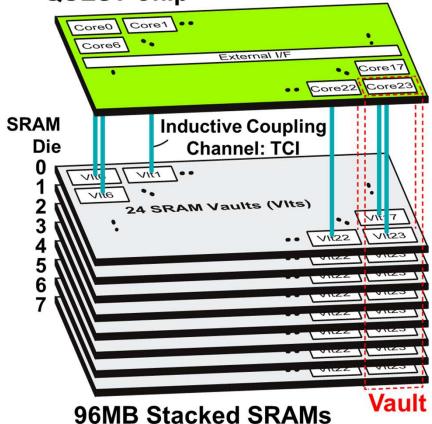

# 実例-2: 本村G 対数量子化-3次元DNNチップ

### **QUEST Chip**

- □ 対数量子化近似DNN推論エンジン

- 枝刈りによる不規則 & スパース NNがターゲット

- 7.49TOPS(バイナリ時)

# **ISSCCで発表** (18年2月)

世界初の対数量子化・3次元積 層DNNチップ。Silkroad Award受賞。日経新聞等掲載

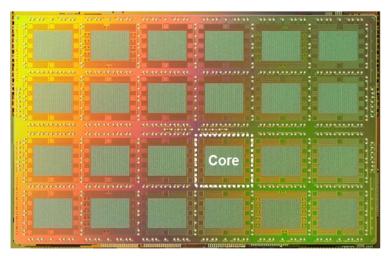

# 実例-3: ルネサスエレ社 DRP-AIチップ

SRAM (2MByte)

SRAM (2MByte)

SRAM (2MBvte)

SRAM (2MByte)

SRAM (2MByte)

SRAM (2MBvte)

I-MAC

(1024)

STP3

(DRP)

DRP: 動的再構成プロセッサ

画像を使ったe-AIを実現する DRP搭載マイクロプロセッサ「RZ/A2M」

(2018年10月ルネサスエレ社広報)

# VLSIシンポジウムで発表

(18年6月)

**日本企業初**のAIチップ学会発表(北大も共著で参加)。リコンフィギュラブルハードウェアAIチップの世界的代表例

- ユーザカスタマイズAI処理

- 実応用性能

を訴求

# AIチップ: 世界の状況

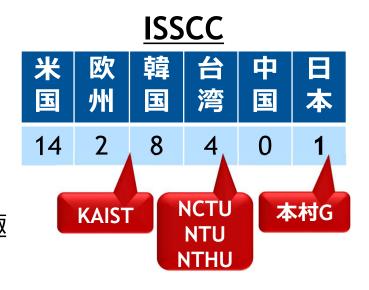

- □ トップ国際会議 ISSCC及びVLSI シンポジウムでのAIチップ関連 の発表 ('16~'18)

- 殆どは大学・公的研究機関

- 米国が圧倒的な強さを発揮

- 韓国はKAIST 1 極、台湾は国立大学 3 極

- 中国勃興の兆し

- 日本の存在感低し

# VLSIシンポジウム

- ロ チップ設計試作支援の存在感

- 米国 DARPAのCRAFTプロジェクト

- 台湾 CIC (Chip Impl. Center)

- □ 両社ともTSMC16nm最先端CMOSによる チップ試作(~2億円)をフルサポート

- => ただ同然で試作

# ISSCC2018:機械学習分野の技術的特徴

|              | セッション名 →     | NM.         | Deep Learning and |           |           |              | Ext.         | Computation in Memory |             |              |          |          |

|--------------|--------------|-------------|-------------------|-----------|-----------|--------------|--------------|-----------------------|-------------|--------------|----------|----------|

| ↓技           | 術分類項目        | 7.4         | 13.2              | 13.3      | 13.4      | 13.5         | 21.2         | 31.1                  | 31.2        | 31.3         | 31.4     | 31.5     |

| 上            | 深層NN         |             | 1                 | ~         | <b>✓</b>  | ~            | <b>✓</b>     | ~                     |             |              | ~        | ~        |

| 技            | Binary       |             | <b>'</b>          | ~         |           | V            |              | ~                     |             |              | ~        | ~        |

| Ξ            | 量子化          |             | Log               | 線形        |           |              |              |                       |             |              |          |          |

| 対象ML技術       | その他ML        | NM          |                   |           |           |              |              |                       | SVM         | HD           |          |          |

| 採            | 特徴           | 学習          | 汎用                | 汎用        |           |              |              |                       | 学習          | 学習           |          |          |

| ÆIJ          | インメモリ        |             | <b></b>           |           |           | V            |              | V                     | <b>✓</b>    |              | <b>v</b> | ~        |

| X            | メモリ積層        |             | 磁界                |           |           |              |              |                       |             |              |          |          |

| 浴/ch.        | Mixed-Signal | <u>v</u>    |                   |           |           | <u></u>      | <b>✓</b>     | <u>V</u>              |             | <u>v</u>     | 1        |          |

| 回路/<br>Tech. | Non CMOS     |             |                   |           |           |              |              |                       |             | CNT          | ReR      |          |

|              | 発表機関         | Geor<br>gia | 北大                | KAIS<br>T | KAIS<br>T | Stanf<br>ord | Colu<br>mbia | MIT                   | Illino<br>i | Stanf<br>ord | NTH<br>U | NTH<br>U |

凡例

汎用: CNN, RNN, MLP, 等の種々のDNNに対応可能

NN: ニューラルネット 磁界: 磁界結合データ転送

NM: ニューロモルフィック SVM: サポートベクトルマシーン

学習: 強化学習 HD: ハイパーディメンショナルコンピューティング

Log: 対数量子化CNT: カーボンナノチューブFET線形: 線形量子化ReR: 抵抗変化型メモリ(ReRAM)

# ISSCC2019: 機械学習分野の技術的特徴

|     | セッション名 → Machine Learning |          |               |               |       |            |          | ML &  |           |             | & Com-in-M |        |          |           |

|-----|---------------------------|----------|---------------|---------------|-------|------------|----------|-------|-----------|-------------|------------|--------|----------|-----------|

| 1   | 技術分類項目                    | 7.1      | 7.2           | 7.3           | 7.4   | 7.5        | 7.6      | 7.7   | 14.2      | 14.3        | 14.4       | 24.1   | 24.4     | 24.5      |

|     | 深層NN                      | •        | •             |               | •     | ~          |          | •     | •         | •           | 1          | V      | V        | V         |

|     | 低ビット量子化                   |          |               |               |       | ~          |          |       |           |             | V          | •      | •        | V         |

| 松   | スパース化                     | V        |               |               |       | 1          |          | 1     |           |             |            |        |          |           |

| M   | その他                       |          | CNN/<br>Image |               | 汎用    | 汎用<br>/FFT |          | 汎用    |           |             | Conv       | Conv   | Conv     | Conv      |

| 対象M | その他ML                     |          |               | <i> </i>      |       |            | NM       |       |           |             |            |        |          |           |

| 11  | 学習対応                      |          |               |               | RL    |            | 新        | DL    |           |             |            |        |          |           |

|     | システム集積<br>化               | モバイ<br>ル | 車載            | ビデオ           | , and |            |          |       |           | マイコン        |            |        |          |           |

| な口  | インメモリ                     |          |               | 100           |       | <b>~</b>   |          |       | ~         |             | V          | •      | •        | V         |

| 回路  | Mixed-Signal              |          |               |               |       |            |          |       |           |             | ~          | ~      | <b>/</b> | V ,       |

|     | 新規デバイス                    |          |               | <i>i</i><br>! |       |            |          |       |           | ReRAM       |            | ReRAM  | /        |           |

|     | 発表機関                      | サムスン     | 東芝            | ミシガ<br>ン大     | KAIST | 清華<br>大    | ソウ<br>ル大 | KAIST | ミシガ<br>ン大 | スタン<br>フォード | テキサ<br>ス大  | 国立精 華大 | 東南大      | 国立精<br>華大 |

- プロセッシング視点: スパース化・学習対応・システム集積化

- 回路技術視点: 低ビット精度・インメモリ・ミックスドシグナル

# AIコンピューティング: プロモーション方策

□ 方策1: AIアーキテクチャ-プロジェクト

□ 方策2: AIチップ-ファーム

□ 方策3: AIコンピューティング-センター

# AIコンピューティング: プロモーション方策

- □ 方策1: AIアーキテクチャ-プロジェクト

- **システムアウェア**なAIハードウェアの研究

- □製造技術に依存しないファブレス型研究

- <u>産学連携プロジェクト群</u>で応用-アルゴリズム -アーキテクチャ縦断エコシステムの形成

- □ 方策2: AIチップ-ファーム

□ 方策3: AIコンピューティング-センター

# 経産省: AIチップ・次世代コンピューティング関連事業 (NEDO, 2018~)

# 高効率・高速処理を可能とするAIチップ・次世代コンピューティングの技術開発事業 平成30年度予算額 100.0億円(新規)

商務情報政策局 情報産業課 03-3501-6944

### 事業の内容

### 事業目的·概要

- IoT社会の到来で急増した情報を活用するためには、革新的なセンサ技術などで効率的に情報を活用するだけでなく、ネットワークの未端(エッジ)側で中心的な情報処理を行うエッジコンピューティング等、従来のサーバー(クラウド)集約型から情報処理の分散化を実現することが不可欠です。

- 半導体の開発指標たるムーアの法則の終焉が叫ばれ、既存技術の延長は限界を迎えつつあります。他方、エッジ側でAI処理を実現するため、小型かつ省エネルギーながら高度な処理能力をもった専用チップと、それを用いたコンピューティング技術が必要です。また、クラウド側でも増加が著しいデータの処理電力を劇的に低減するため、従来の延長線上にない新しい技術の実現が求められます。

- 本事業は、エッジ側で超低消費電力AIコンピューティングや、新原理により 高速化と低消費電力化を両立する次世代コンピューティング等、ソフトだけ ではなくハードと一体化した技術開発を実施。ポストムーア時代における我 が国のベンチャーを含む情報産業の競争力強化、再興を目的とします。

### 成果目標

平成30年度から最長で平成39年度までの10年間の事業であり、IoT社会をエッジからクラウドまで高度化する基盤技術を確立、省電力化を実現します。(平成49年度において約4,900万t/年のCO2削減を目指します。)

### 条件(対象者、対象行為、補助率等)

(研)新エネルギー・産 業技術総合開発機構 (NEDO)

大学·研究 機関·民間 企業等

### 事業イメージ

### 【コネクテッド・インダストリーズの実現】

クラウド×次世代コンピューティング

エッジ×革新的AIコンピューティング

多様な人、組織、機械、技術がつながる社会の基盤技術

### <sup>「</sup>革新的AIエッジコンピューティング技術の開発

- エッジ側では電力等の制限が厳しく、革新的AIチップを用いたエッジAIコンピューティングの省エネ化に関する開発を実施。

- エッジAIコンピューティングの開発では、良質なデータを用いた用途毎の擦り合わせが重要。ソフトとハードを一体化する技術開発等を実施。

### 次世代コンピューティング技術の開発

- ・中期的には高速化と省エネ化を実現するコンピューティング技術開発を実施する。

- 長期的には、現状を打破する破壊的イノベーションの創造に向けた新原理コンピューティングの技術の開発等を実施する。

### 高度なIoT社会を実現する横断的技術開発

大量のデータの効率的かつ高度な利活用を実現する情報の収集、蓄積、解析、 セキュリティ等に関する横断的技術開発を実施する。

# NEDO 「革新的AIエッジコンピューティング 技術の開発」採択12プロジェクト

| テーマのキーワード          | 事業者                                          |

|--------------------|----------------------------------------------|

| エッジHPC、OS          | イーソル、名古屋大                                    |

| 超広範囲センシングAIエッジ技術   | 沖電気、 <del>会津大</del> 、ALSOK、ジャパンマリンユ<br>ナイテッド |

| 5G、高度自律的学習機能       | KDDI、アラヤ                                     |

| 進化型・低消費電力AI エッジLSI | ソシオネクスト、Architek、豊田自動織機                      |

| 動的再構成技術、組み込みAl     | ルネサスエレクトロニクス、三菱電機、<br>SOINN、北大               |

| 完全自動運転SoC          | 東京大、埼玉大、アクセル、ティアフォー                          |

| 不揮発省電力FPGA         | NEC                                          |

| エッジビジョンAI、超軽量化技術   | フィックスターズ                                     |

| 動的多分岐・結合トレース型AI HW | NSITEXE、ユーリカ、日立、東工大                          |

| 横断的なセキュリティ評価       | 産総研、ECSEC、コネクテックジャパン、IIJ<br>イノベーションインスティチュート |

| エッジヘビーAI向けSoC      | Preferred Networks、神戸大                       |

| セキュアオープンアーキテクチャ    | 日立、産総研、慶應大                                   |

# 27

# 文科省: 革新的コンピューティング戦略目標 => CREST/さきがけ (JST, 2018 ~)

戦略的創造研究推進事業

平成30年度 JST戦略的創造研究推進事業(CREST) 「コンピューティング基盤」 提案募集 (第1期)

Society5.0を支える 革新的コンピューティング技術

### 研究総括

坂井修一(さかい しゅういた 東京大学 情報理工学系研究科 2018年4月12日、25日(東京)

2018/4/12, 25

コンピューティング基盤

# AIコンピューティング: プロモーション方策

- □ 方策1: AIアーキテクチャ-プロジェクト

- ■システムアウェアなAIハードウェアの研究

- □製造技術に依存しないファブレス型研究

- 産学連携プロジェクト群で応用-アルゴリズム NEDO事業 -アーキテクチャ縦断エコシステムの形成

- □ 方策2: AIチップ-ファーム

- 先進アーキテクチャを低コスト・短TATで HW化・実証するための**LSI設計試作環境の構築**

- システムアウェアHWプレイヤの育成・放牧

- □ 方策3: AIコンピューティング-センター

産総研・東大 AIチップ設計 拠点

# 東大

システムデザ イン研究セン 夕 (d.lab)

# AIコンピューティング: プロモーション方策

# □ 方策1: AIアーキテクチャ-プロジェクト

- <u>システムアウェア</u>なAIハードウェアの研究

- □製造技術に依存しないファブレス型研究

- 産学連携プロジェクト群で応用-アルゴリズム -アーキテクチャ縦断エコシステムの形成

# □ 方策2: AIチップ-ファーム

- 先進アーキテクチャを低コスト・短TATで HW化・実証するためのLSI設計試作環境の構築

- システムアウェアHWプレイヤの<u>育成・放牧</u>

# □ 方策3: AIコンピューティング-センター

- 既存のAIセンターはAIアルゴリズム・応用にフォーカス

- 上位レイヤと連携するAIハードウェア**中核拠点**が必要

# 日本の産官学はどう取り組むべきか

# AIコンピューティング: 必要な方策

□ 方策1: AIアーキテクチャ-プロジェクト → 経産省・NEDO

- <u>システムアウェア</u>なAI-HW研究

- 産学連携プロジェクト群で応用-アルゴリズム -アーキテクチャ縦断エコシステムの形成

- 方策2: AIチップ-ファーム

- 先進アーキテクチャを低コスト・短TATで HW化・実証するためのLSI設計試作環境の構築

- システムアウェアHWプレイヤの育成・放牧

- 方策3: AIコンピューティング-センター

- 既存のAIセンターはAIアルゴリズムが中心

- システムアウェアAI-HWの**中核拠点**を形成

AIコンピューティング研究ユニット @東京工業大学の狙い

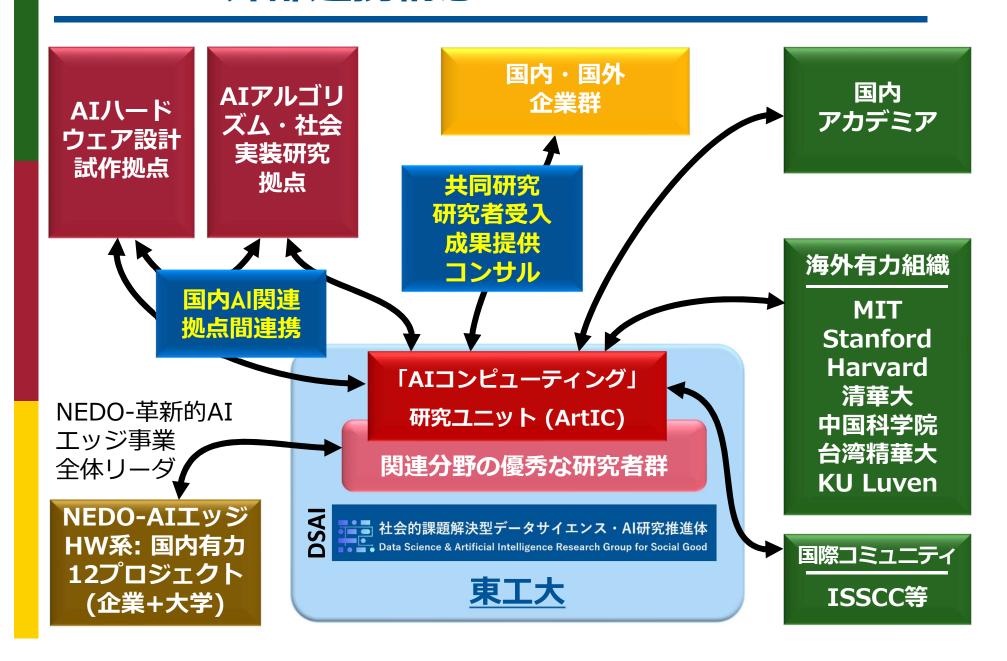

# AIコンピューティング研究ユニット: ArtIC

2019年4月 に発足 2020年4月からフル メンバで活動予定

10/1に阪大から劉 (Yu)准教授を迎え,研 究活動を本格化.**研究** スタッフも募集中 すずかけ 台キャン パス J3棟 17F

# http://www.artic.iir.titech.ac.jp

# ArtIC: 研究ターゲット

人工知能(AI)応用の急速な拡大 「**コントロール**駆動から**データ**駆動へ」 **計算機アーキテクチャの革命**

組合せ最適化問題 → スピン格子のエネル ギー最小化問題

<u>大量データの学習 →</u> 強力な推論・識別・予測能力

抽象シナプス 抽象ニューロン

深層ニューラルネット ・ディープラーニング 説明性・制御性の高さと低学習負荷の両立

アニーリング計算機 (非量子)

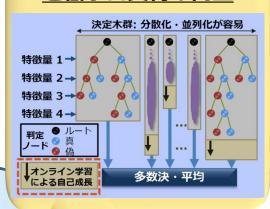

・統計的機械学習 ▼ (アンサンブル学習等)

構造型情報処理アーキテクチャ として共通基盤化

アルゴリズム理解 => アーキテクチャ研究 => ハードウェア実現

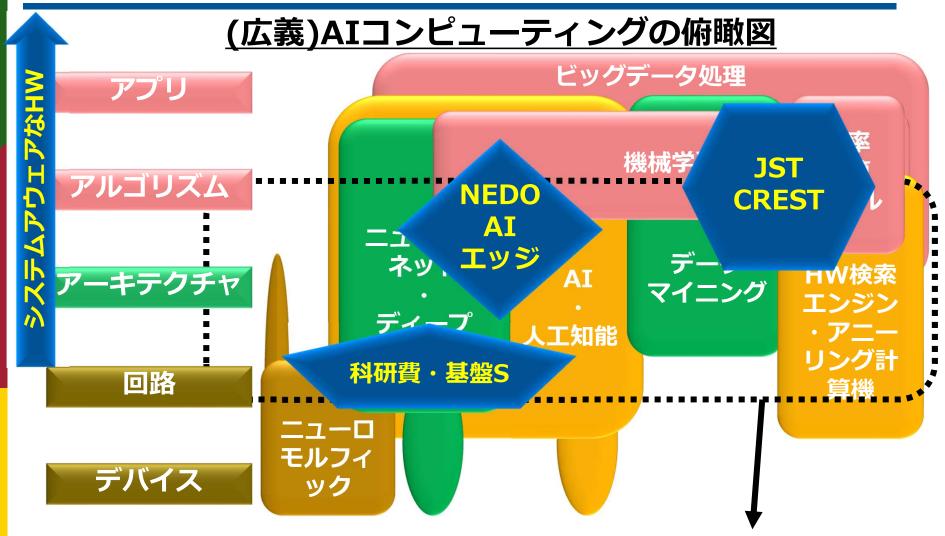

# ArtIC: 研究アプローチ (Society5.0観点で)

- 深層ニューラルネット -

- より広範な機械学習 -

- AIコンピューティング

- 組合せ最適化・列挙 -

- アニーリング計算 -

- グラフマイニング -

アーキテクチャ

# ArtIC: 研究分野・研究レイヤ

これら広範囲のAIコンピューティング群を加速する アーキテクチャプラットフォームの研究を推進する

# ArtIC: 外部連携構想

# 注目すべき研究トレンド

# □ DNNアクセラレータは更なる変革期へ

- 推論単体:

- □ 疎結合性の活用が進行中

- □ 非畳み込み型DNNの勃興

- 学習アルゴリズム-アーキテクチャ協創

- □バックプロパゲーション離脱の試み

- エッジ学習・オンライン学習への取り組み

- アテンション技術のアーキテクチャ展開

# □ DNNアクセラレータ as a モジュール

- 上位システムアーキテクチャへの展開

- 従来機械学習手法との融合・適材適所

- Explainable AI

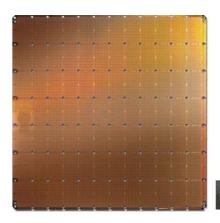

### Cerebras社: Wafer Scale Engine

21.5 cm

- 構造型情報処理アプローチ

- All SRAM

# □ 非線形・確率的コンピューティングへの展開

- 最適化アクセラレータ・アニーリングチップ

- □ 非量子,集積回路ベースの研究活性化

- □ 日本のアクティビティが高い分野

# AI:= コンピューティングのゲームチェンジャ

# ロ AIチップへのゴールドラッシュ

- 計算機アーキテクチャ研究者がこの分野に集結

- Re-Inventing Computer

# □ What is Next Exponential (指数関数的増大)?

- ムーアの法則は続くのか?

- メモリ容量/チップ, CPU性能/チップの次はあるのか?

- **私見: ニューロン数/チップ ないしは AI性能/チップが次の指標に**

# □日本は周回遅れ

- システムアウェアハードウェアへのR&D投資が中抜け状態

- しかし、本来の技術蓄積は厚い

- □AI分野は元来日本の得意分野

# □ 「遅い?」=> Yes. 「遅すぎ?」=> No.

- 現在のAIブームは「氷山の一角」

- 変化の激しさ => 後発者利益を取り得る分野

- ゲームチェンジ => 日本にとっての再チャンス

# AIコンピューティング: 日本の活きる道

# □ アイデアの先回り

- 程よいジャンプ感

- 飛ぶ距離と飛ぶ方向を間違わない

- 集合知の強みを活かす

# □出口 = 組み込みシステム

- アジェンダ設定の「戦略」

- 勝てる枠組みを作る・使う

# □ 蓄積材活用

- ■人材・知財

- □ 10 20年前のアイデアがようやくmake sense

- 時間を買う

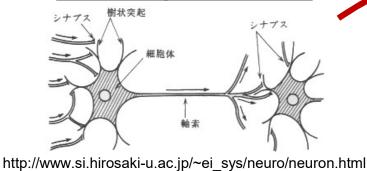

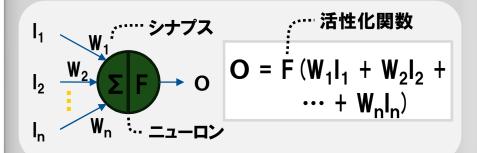

# 脳模倣型情報処理とディープラーニング

# シナプス/ニューロン

# ロ スパイキングニューロン

- 生理学モデルをなるべく忠実に電子回路化

- パルス列で信号を表現

- アナログ的に蓄積=>発火

- => <u>ニューロモルフィック</u>

- => 脳模倣・エミュレーション

# 積和型ニューロン

- 計算機上で処理しやすいように 抽象化したモデル

- 単なる乗算と加算

- => <u>ニューラルネット</u>

- => 機械学習の分類器としても広く 利用されている

# 脳模倣型情報処理

"鳥"を目指す

別物/ 別時間軸

# ディープラーニング

"飛行機"を目指す

# 脳模倣型情報処理とディープラーニング

# 脳模倣型情報処理

"鳥"を目指す

何が本質? 実現可能?

# ディープラーニング

"飛行機"を目指す

| ۱۱ <u>=</u> ۲۲       | 比較項目          | "飛行機"                                     |

|----------------------|---------------|-------------------------------------------|

| 自然界が<br>作り上げた<br>お手本 | 位置づけ          | 鳥に学び、「飛ぶこと」の本<br>質を残し、工学的に実現方法<br>な枠組みを構築 |

|                      | エネルギー<br>効率   | A飛行機が社会<br>にもたらした<br>変革の本質                |

| ×                    | 大量輸送/<br>高速輸送 |                                           |

# AIコンピューティング: 米国+中国が圧倒

# □ 米国

必ずしもチップ実装まで行わない ハードウエア方式レベルの研究も含む

- NVIDA, Google, Apple,,,

- AIハードウェア系スタートアップ多数

- DARPA: ERI(Electronics Resurgence Initiative) 2018~

- □ 年間**200億円**を超える予算

- **リコンフィギュラブル**ハードウェア

- **ドメインスペシフィック** チップ

- HW設計のモジュール化・スマート化

- **オープンソース**ハードウェア

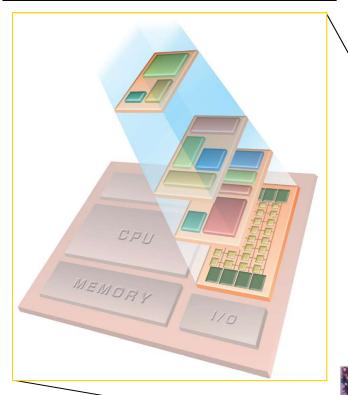

- 3次元集積 System-on-a-chip

- 非ノイマンコンピューティングデバイス

# □ 中国

- **年間1,000億円規模の**AIハードウェア国家Pj

- □ 清華大・中国科学院にAIハードウェアセンタ

- 一説には約30社のAIチップスタートアップ企業が存在

# AIチップ設計拠点への期待

- □ チップ化の重要性

- アイデアを形に (プロトタイピング)

- リアリティによる説得力

- 現実制約との折り合い

ハードウェ アなんて分 からない

- □ 活動範囲

- 設計検証ツール・インフラ

- IPコアの提供

- 設計サービス

- 試作サービス

ファンダリ利用の ターンキー

- □ as a Serviceの視点から構築

- □ AIエッジ等、他プロジェクトとの連携

チップ化して初めて 競争の土俵に上がれる

AI応用の専門家、AIア ルゴリズムの専門家を チップ化に呼び込むに は?

AIチップ設計拠点 ↓ AIチップ設計・<u>試</u> 作・サービス拠点